Bei moderner Digitaltechnik spielen die Leistungsaufnahme (Energieverbrauch) und die Wärmeentwicklung eine immer größere Rolle. Die CMOS-Technik trägt grundlegend dazu bei, diese herabzusetzen. CMOS steht dabei für "komplementäre Metalloxid-Halbleiter" (englisch: complementary metal oxide semiconductor) und beschreibt damit schon das Prinzip: Es werden zueinander komplementäre (also entgegengesetzt gerichtete) MOSFETs genutzt, wobei immer jeweils nur einer von beiden leitend ist und der andere sperrt. So fließt im Betrieb so gut wie kein Strom, lediglich beim Umschaltvorgang.

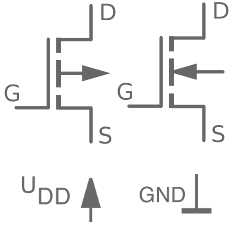

Die wichtigsten Elemente sind die MOSFETs (siehe Abb. oben). Diese steuern die Verbindung zwischen S und D. Im Normalfall sperren sie. Wenn zwischen G und dem mit dem Pfeil gekennzeichneten Anschluss eine richtig gepolte Spannung anliegt, leiten sie. Dabei muss das höhere Potential in Richtung der Pfeilspitze anliegen. Für eine genauere Erklärung sei auf das Kapitel über MOSFETs verwiesen.

Die wichtigsten Elemente sind die MOSFETs (siehe Abb. oben). Diese steuern die Verbindung zwischen S und D. Im Normalfall sperren sie. Wenn zwischen G und dem mit dem Pfeil gekennzeichneten Anschluss eine richtig gepolte Spannung anliegt, leiten sie. Dabei muss das höhere Potential in Richtung der Pfeilspitze anliegen. Für eine genauere Erklärung sei auf das Kapitel über MOSFETs verwiesen.

In die gesamte Schaltung wird eine Leitung mit dem definierten Potential 0 Volt gelegt. Um nicht die kompletten Leitungen bis zur Spannungsquelle zeichnen zu müssen, wird das GND-Symbol (siehe Abb. unten rechts) genutzt. Dieses kann natürlich auch mehrfach auftreten. Alle dort angeschlossenen Leitungen haben das Potential 0 Volt.

Neben der GND-Leitung gibt es eine weitere Leitung. Zwischen dieser und der GND-Leitung wird eine Versorgungsspannung UDD angelegt. Da diese Leitung überall in der Schaltung gebraucht wird, wird auch diese mit einem Symbol dargestellt (siehe Abb. unten links).

In der nebenstehenden Animation wird die Funktionsweise der CMOS-Technologie beispielhaft am Inverter erklärt, also einem Bauteil, das seinen Eingang umkehrt. Die logischen Werte wahr und falsch werden dabei mit der Versorgungsspannung (für wahr) bzw. dem Null-Potential (für falsch) dargestellt.